Mt2015-q4

Mt2015-q4

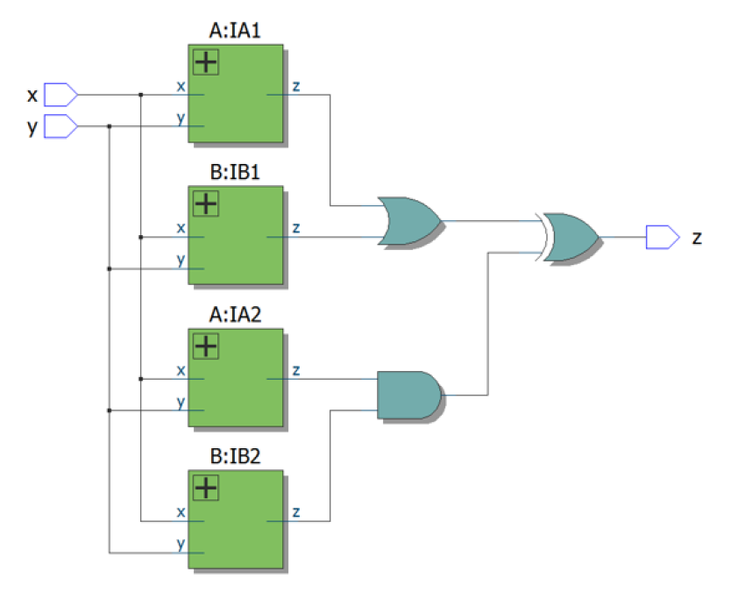

The top-level design consists of two instantiations each of subcircuits A and B, as shown below.

hint

You may choose to create this circuit hierarchically using the two submodules as shown in the diagram, or create the same functionality without hierarchy.

solution

1 | |

Mt2015-q4

http://456-xiao.github.io/2024/09/07/Mt2015-q4/